62

# R/W Operation & Performance Analysis of 4T & 6T SRAM

Rajkumar Sarma\*

VLSI Design, SEEE, Lovely Professional University, Phagwara, Punjab, rajkumar.16886@lpu.co.in

Abstract: A detailed analysis on different approaches of designing sense amplifier is discussed in this paper. 4T & 6T SRAM cells are implemented in cadence virtuoso 90 nm CMOS technology along with differential and current mirror sense amplifiers. The result suggests that the Current Mirror Sense Amplifier (CMSA) is better option in terms area along with high speed although at the cost of 50 % more power consumption than Differential Sense Amplifier (DSA).

Keywords: Current Mirror, CMOS, SRAM, Cadence Virtuoso

# I. INTRODUCTION

SRAM is a memory unit to store data. As its name indicates, it stores till the power supply is on [6]. Unlike DRAM does not require periodic refreshments and it uses two inverters to store data and a sense amplifier for the retrieval of data when it is necessary. Power consumption of SRAM depends upon many factors but the most important one is that "how many times the bit line is accessed in a cycle".

Each SRAM cell is made up of 4 transistors used to store data, which are basically two cross coupled inverter circuits. These inverter circuits have two stable states either '0' or '1'. Two more transistors are used to access the data during read and write operation. It has three modes of operation named as hold, read and write operations.

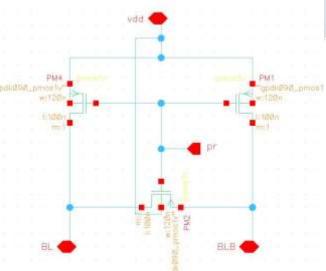

## A. Pre-charge Circuit

The pre-charge circuit has only one use in SRAM. The function of SRAM circuit is to charge the BL and BLB to vdd=1.8 volts. With the help of pre-charge circuit SRAM keeps the BL and BLB all the times high except during read and write operation. The width used for PMOS is 2.4u and length used is equals 180n.

Fig. 1. Design of Pre-chanrge Circuit in CMOS 90nm

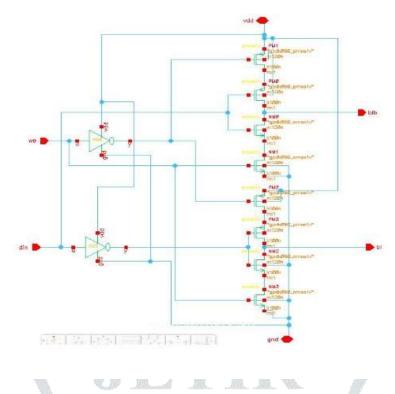

## **B.** Write Driver Circuit

It starts with data to be written on bit lines. Suppose to write '0' then '0' must be applied to BL and its complement to BLB. In write operation two not gates are connected back to back whose output worked for controlling voltage of two NMOS transistors which further attached to two access transistors for write enable pin. When both the pins get high it performs the write operation.

Fig. 2. Design of Write Driver Circuit in CMOS 90nm

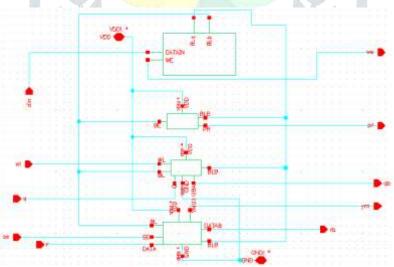

# C. Single Bit Memory Cell using 6T

It comprises of SRAM cell, pre-charge circuit, write driver circuit, sense amplifier and column select. The complete schematic is shown below. This schematic shows all the different peripherals circuit combined with SRAM cell, to form a complete SRAM read and write operation. The input signals are WE that allows the writing operation, SE that allows reading from SRAM cell & WL that allows to decide from which address data will be written or read & the signal data either 0 or 1 is to be stored or read from the cell.

Fig. 3. Design of Single Bit Memory Cell using 6T in CMOS 90nm

# II. POWER, DELAY & AREA ANALYSIS OF 4T & 6T SRAM CELLS

Using this 4T SRAM memory system area consumption is significantly reduced by an amount of 40% as compare to existing 6T SRAM as shown in table-I. Power dissipation is a component to think in 4T SRAM (as shown in table II & III) about since it dissipates 50% more power than conventional 6T.

www.jetir.org (ISSN-2349-5162)

| Table- I: Area calculation of 6T & 4T |              |        |  |

|---------------------------------------|--------------|--------|--|

| Serial                                | Type of SRAM | Area   |  |

| 1                                     | 4T Cell      | 94.14  |  |

| 2                                     | 6T Cell      | 154.17 |  |

#### Table- II: PDP calculation of 4T

| Supply voltage | Delay (ns) |       | Power dissipation(µW) | PDP                    |

|----------------|------------|-------|-----------------------|------------------------|

|                | Read       | Write |                       | FDF                    |

| 0.5 V          | 25.11      | 0.34  | 1.23                  | $0.031 \times 10^{18}$ |

| 1 V            | 20.30      | 0.193 | 19.56                 | $0.400 \times 10^{18}$ |

| 1.5 V          | 20.01      | 0.183 | 65.15                 | $1.315 \times 10^{18}$ |

| 2 V            | 19.90      | 0.113 | 145.5                 | 2.911×10 <sup>18</sup> |

#### Table- III: PDP calculation of 6T

| Supply voltage | Delay (ns) |       | Power dissipation(µW) | מכום                  |

|----------------|------------|-------|-----------------------|-----------------------|

|                | Read       | Write |                       | PDP                   |

| 0.5 V          | 5.082      | 0.173 | 0.215                 | $1.12 \times 10^{15}$ |

| 1 V            | 0.335      | 0.162 | 3.13                  | $1.53 \times 10^{15}$ |

| 1.5 V          | 0.210      | 0.151 | 11.71                 | $4.22 \times 10^{15}$ |

| 2 V            | 0.145      | 0.133 | 142.1                 | 39.5×10 <sup>15</sup> |

Fewer transistors will always be welcomed in designing high density SRAM arrays. In 4T data and their compliment has been held on each node unlike in 6T where two coupled inverters are used to hold the single bit data. On the basis of above results one can clearly say that 4T saves around 40% area to perform the same operation but at cost of 60 % extra power dissipation.

# III. PERFORMANCE ANALYSIS OF DIFFERENT SENSE AMPLIFIERS

| Table- IV: De   | elay calculation of DS | SA & CMSA |  |

|-----------------|------------------------|-----------|--|

|                 | Delay (ns)             |           |  |

| V <sub>DD</sub> | <b>D</b> SA            | CMSA      |  |

| 0.5 V           | 3.22                   | 0.68      |  |

| 1 V             | 0.361                  | 0.064     |  |

| 1.2 V           | 0.316                  | 0.084     |  |

| 1.5 V           | 0.257                  | 0.027     |  |

| 1.8 V           | 0.226                  | 0.013     |  |

| 2 V             | 0.116                  | 0.010     |  |

## Table- V: Power Calculation of DSA & CMSA

|                 | Power Dissipation (µW) |       |  |

|-----------------|------------------------|-------|--|

| V <sub>DD</sub> | DSA                    | CMSA  |  |

| 0.5 V           | 1.365                  | 2.01  |  |

| 1 V             | 27.94                  | 29.9  |  |

| 1.2 V           | 53.15                  | 55.27 |  |

| 1.5 V           | 60.75                  | 112.1 |  |

| 1.8 V           | 103.6                  | 198.9 |  |

| 2 V             | 140.01                 | 277.7 |  |

| Table- VI: Area Calculat | ion of DSA & CMSA |

|--------------------------|-------------------|

|--------------------------|-------------------|

| Serial<br>no. | Type of<br>Sense | Area<br>(mm <sup>2</sup> ) |

|---------------|------------------|----------------------------|

| 1             | DSA              | 187.42                     |

| 2             | CMSA             | 112.03                     |

As it is visible from table-IV that as the power supply get increased the delay gets reduced and power dissipation increases. Now on the basis of the analysis it is clearly visible that at 1V supply voltage, CMSA delay is 0.064 ns while DSA delay is 3.22 ns. The delay of CMSA circuit is 82.3 % lesser than that of DSA circuit. That means CMSA has better speed than conventional DSA.

Table-V shows the power dissipation by both kind of sense amplifiers. Clearly DSA has less power dissipation than CMSA. For 2V supply voltage it consumes almost 50 % less power than CMSA. As per area regard CMSA saves almost 40 % area as compared to DSA (table-VI).

#### **IV.** CONCLUSION & FUTURE SCOPE

A detailed analysis on different approaches of designing sense amplifier is discussed in this paper. 4T & 6T SRAM cells are implemented in cadence virtuoso 90 nm CMOS technology along with differential and current mirror sense amplifiers. On the basis of these three important parameters it can be concluded that CMSA is better option in terms area along with high speed although at the cost of 50 % more power consumption.

In coming future there is a lot of work can be done in the field of SRAM in terms of designing SRAM cell with reduced number of transistors with ultralow power dissipation. The feasibility of 2T and single transistor SRAM cells can also be evaluated as it can highly improve the density of SRAM array which is a major problem in present day. Also, one can work on making fast sense amplifiers which contribute to less delay and speed up the performance of the SRAM system.

#### REFERENCES

- H. Fujiwara et al., "Novel video memory reduces 45% of bit line power using majority logic and data-bit reordering," IEEE Trans. Very Large- Scale Integr. (VLSI) Syst., vol. 16, no. 6, pp. 620–627, Jun. 2008

- 2. H. Noguchi, Y. Iguchi, H. Fujiwara, Y. Morita, K. Nii, H. Kawaguchi, and M. Yoshimoto, "A 10T non-precharge two-port SRAM for 74% power reduction in video processing," in Proc. IEEE Computer Society Annual Symp. VLSI (ISVLSI), March 2007, pp. 107–112.

- 3. A. Kawasumi, T. Suzuki, S. Moriwaki, and S. Miyano, "Energy efficiency degradation caused by random variation in low-voltage SRAM and 26% energy reduction by Bitline Amplitude Limiting (BAL) scheme," in Proc. IEEE Asian Solid-State Circuits Conf., Nov. 2011, pp. 165, 168.

- 4. H. Mostafa, M Anis, and M. Elmasry. "Statistical SRAM read access yield improvement using negative capacitance circuits." *IEEE Transactions on Very Large-Scale Integration (VLSI) Systems* 21.1 (2011): 92-101.

- 5. X. Chen and L.S. Peh. "Leakage power modeling and optimization in interconnection networks." *Proceedings of the 2003 international symposium on Low power electronics and design*. ACM, 2003.

- 6. A. Andrei, et al., "Overhead-conscious voltage selection for dynamic and leakage energy reduction of timeconstrained systems." *IEE Proceedings-Computers and Digital Techniques* 152.1 (2005): 28-38

- 7. S. Mutoh, "1-V Power Supply High-speed Digital Circuit Technology with Multi threshold-Voltage CMOS, IEEE Journal of Solis-State Circuits, Vol. 30, No. 8, pp. 847-854, August 1995.

- 8. S. Hassan, I. Dayah, and S. Ili, "Comparative study on 8T SRAM with different type of sense amplifier." 2014 IEEE International Conference on Semiconductor Electronics (ICSE2014). IEEE, 2014.

- 9. J. Zhu, N. Bai, and J. Wu, "A Review of Sense Amplifiers for Static Random-Access Memory," IETE Technical Review vol. 30, no. 1, 2013.

- 10. S. IIi Shairah A. Halim,"Comparative study on cmos SRAM sense amplifier using 90nm techology" *Intenational Conference On Technology Indonesia* june 23-26 2013.

- M. Sinha; S. Hsu; A. Atila, B. Wayne, R.Krishnamurthy, S. Borhr, "High-Performance and Low Voltage Sense-Amplifier Techniques for sub-90nm SRAM", *IEEE International [Systems-on-Chip] SOC Conference*, pp. 113 - 116, 2003.

- L. H. Chun and M. H. Ho, "High-Speed Sense Amplifier for SRAM Applications", The 2004 IEEE Asia-Pacific Conference on Circuits and Systems, pp. 577 - 580,2004.